# 1 GSPS Direct Digital Synthesizer

AD9858

#### **FEATURES**

1 GSPS internal clock speed

Up to 2 GHz input clock (selectable divide-by-2)

Integrated 10-bit DAC

Excellent phase noise and SFDR

32-bit programmable frequency register

Simplified 8-bit parallel and SPI serial control interface

Automatic frequency sweeping capability

4 frequency profiles

3.3 V power supply

Power dissipation: 2 W typical

Integrated programmable charge pump and phase frequency detector with fast lock circuit Isolated charge pump supply up to 5 V Integrated 2 GHz mixer

### **APPLICATIONS**

VHF/UHF LO synthesis

Tuners

Instrumentation

Agile clock synthesis

Cellular base station hopping synthesizers

Radars

SONET/SDH clock synthesis

#### **GENERAL DESCRIPTION**

The AD9858 is a direct digital synthesizer (DDS) featuring a 10-bit digital-to-analog converter (DAC) operating up to 1 GSPS. The AD9858 uses advanced DDS technology coupled with an internal high speed, high performance DAC to form a digitally programmable, complete high frequency synthesizer capable of generating a frequency-agile analog output sine wave at up to 400 MHz. The AD9858 is designed to provide fast frequency hopping and fine tuning resolution (32-bit frequency tuning word). The frequency tuning and control words are loaded into the AD9858 via parallel (8-bit) or serial loading formats. The AD9858 contains an integrated charge pump (CP) and phase frequency detector (PFD) for synthesis applications requiring the combination of a high speed DDS along with phase-locked loop (PLL) functions. An analog mixer is also provided on chip for applications requiring the combination of a DDS, PLL, and mixer, such as frequency translation loops and tuners. The AD9858 also features a divide-by-2 on the clock input, allowing the external reference clock to be as high as 2 GHz.

The AD9858 is specified to operate over the extended industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

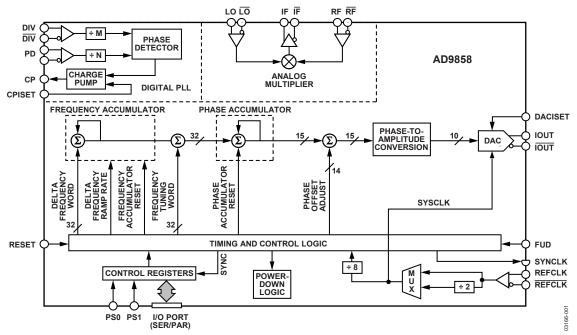

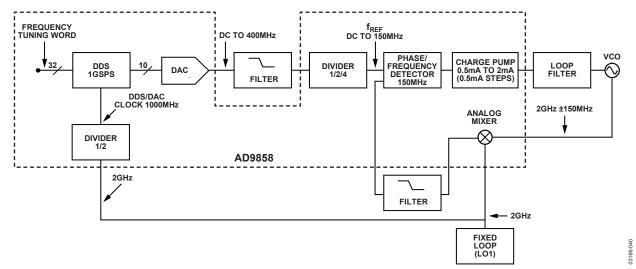

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Rev. C Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

| TABLE OF CONTENTS                                                                                    |                                                                                                               |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Features                                                                                             | Component Blocks14                                                                                            |

| Applications                                                                                         | Modes of Operation 10                                                                                         |

| General Description                                                                                  | Synchronization1                                                                                              |

| Functional Block Diagram                                                                             | Programming the AD98581                                                                                       |

| Revision History                                                                                     | Register Map22                                                                                                |

| Electrical Specifications                                                                            | Register Bit Descriptions                                                                                     |

| •                                                                                                    | -                                                                                                             |

| Absolute Maximum Ratings                                                                             | Other Registers                                                                                               |

| Thermal Performance 6                                                                                | User Profile Registers                                                                                        |

| Explanation of Test Levels6                                                                          | Applications Information                                                                                      |

| ESD Caution6                                                                                         | Evaluation Boards                                                                                             |

| Pin Configuration and Function Descriptions7                                                         | Outline Dimensions                                                                                            |

| Typical Performance Characteristics9                                                                 | Warning                                                                                                       |

| Theory of Operation                                                                                  | Ordering Guide                                                                                                |

| REVISION HISTORY 2/09—Rev. B to Rev. C Changes to Features Section, General Description Section, and | Changes to Delta Frequency Tuning Word (DFTW) Section,<br>Delta Frequency Ramp Rate Word (DFRRW) Section, and |

| Figure 1 1                                                                                           | Phase Offset Control Section                                                                                  |

| Changes to Table 1                                                                                   | Changes to Profile Selection Section                                                                          |

| Changes to Table 26                                                                                  | Deleted Frequency Tuning Control Section                                                                      |

| Added Thermal Performance Section                                                                    | Changed AD9858 Application Suggestions Section to                                                             |

| Changes to Figure 3, Figure 4, and Figure 59                                                         | Applications Information Section27                                                                            |

| Changes to Figure 9, Figure 10 Caption, Figure 11 Caption,                                           | Changes to Table 13                                                                                           |

| Figure 13, and Figure 14                                                                             | Added Exposed Paddle Notation to Outline Dimensions 25                                                        |

| Changes to Figure 17                                                                                 |                                                                                                               |

| Changes to Theory of Operation Section and DAC Output                                                | 4/07—Rev. A to Rev. B                                                                                         |

| Section                                                                                              | Changed EPAD to TQFP_EPUniversa                                                                               |

| Changes to Charge Pump Section                                                                       | Updated Outline Dimensions                                                                                    |

| Changes to Modes of Operation Section                                                                |                                                                                                               |

| Changes to Single-Tone Mode Section and Frequency Sweeping                                           | 11/03—Rev. 0 to Rev. A                                                                                        |

| Mode Section                                                                                         | Changes to Specifications                                                                                     |

| Changes to SYNCLK and FUD Pins Section and Figure 33 18                                              | Moved ESD Caution to                                                                                          |

| Changes to I/O Port Functionality Section, Parallel                                                  | Moved Pin Configuration to                                                                                    |

| Programming Mode Section, and Figure 3520                                                            | Moved Pin Function Description to                                                                             |

| Changes to Figure 36 and Serial Programming                                                          | Changes to Equations                                                                                          |

| Mode Section21                                                                                       | Changes to Delta Frequency Ramp Rate Word (DFRRW) 23                                                          |

| Changes to Table 6                                                                                   | - · · · · · · · · · · · · · · · · · · ·                                                                       |

| Changes to Control Function Register (CFR) Section                                                   | 4/03—Revision 0: Initial Version                                                                              |

| Changes to CFR[21]: Load Delta Frequency Timer Section 24                                            |                                                                                                               |

| Changed CFR[14]: Sine/Cosine Select Bit Section to CFR[14]:                                          |                                                                                                               |

| Enable Sine Output Bit Section                                                                       |                                                                                                               |

# **ELECTRICAL SPECIFICATIONS**

Unless otherwise noted,  $V_{DD}$  = 3.3 V  $\pm$  5%,  $CPV_{DD}$  = 5 V  $\pm$  5%,  $R_{SET}$  = 2 k $\Omega$ , CPISET = 2.4 k $\Omega$ , reference clock frequency = 1 GHz.

Table 1.

| Parameter                                                         | Temp | Test Level | Min                    | Тур      | Max             | Unit  |

|-------------------------------------------------------------------|------|------------|------------------------|----------|-----------------|-------|

| REF CLOCK INPUT CHARACTERISTICS <sup>1</sup>                      |      |            |                        |          |                 |       |

| Reference Clock Frequency Range (Divider Off)                     | Full | VI         | 10                     |          | 1000            | MHz   |

| Reference Clock Frequency Range (Divider On)                      | Full | VI         | 20                     |          | 2000            | MHz   |

| Duty Cycle at 1 GHz                                               | 25°C | V          | 42                     | 50       | 58              | %     |

| Input Capacitance                                                 | 25°C | V          |                        | 3        |                 | рF    |

| Input Impedance                                                   | 25°C | IV         |                        | 1500     |                 | Ω     |

| Input Sensitivity                                                 | Full | VI         | -20                    |          | +5              | dBm   |

| DAC OUTPUT CHARACTERISTICS                                        |      |            |                        |          |                 |       |

| Resolution                                                        | Full |            |                        | 10       |                 | Bits  |

| Full-Scale Output Current                                         | Full |            | 5                      | 20       | 40              | mA    |

| Gain Error                                                        | Full | VI         | -10                    |          | +10             | % FS  |

| Output Offset                                                     | Full | VI         |                        |          | 15              | μΑ    |

| Differential Nonlinearity                                         | Full | VI         |                        | 0.5      | 1               | LSB   |

| Integral Nonlinearity                                             | Full | VI         |                        | 1        | 1.5             | LSB   |

| Output Impedance                                                  | Full | VI         |                        | 100      |                 | kΩ    |

| Voltage Compliance Range                                          | Full | VI         | AV <sub>DD</sub> – 1.5 |          | $AV_{DD} + 0.5$ | V     |

| Wideband SFDR (DC to Nyquist)                                     |      |            |                        |          |                 |       |

| 26 MHz f <sub>оит</sub>                                           | Full | V          |                        | 70       |                 | dBc   |

| 65 MHz fout                                                       | Full | V          |                        | 66       |                 | dBc   |

| 126 MHz fout                                                      | Full | V          |                        | 62       |                 | dBc   |

| 375 MHz fout                                                      | Full | V          |                        | 58       |                 | dBc   |

| 180 MHz fout (700 MHz REFCLK)                                     | Full | IV         | 52                     | 30       |                 | dBc   |

| Narrow-Band SFDR <sup>2</sup>                                     | l an | '          | 32                     |          |                 | u b c |

| 40 MHz f <sub>OUT</sub> (±15 MHz)                                 | Full | V          |                        | 82       |                 | dBc   |

| 40 MHz f <sub>OUT</sub> (±1 MHz)                                  | Full | V          |                        | 87       |                 | dBc   |

| 40 MHz f <sub>001</sub> (±50 kHz)                                 | Full | V          |                        | 88       |                 | dBc   |

| 100 MHz f <sub>OUT</sub> (±35 MHz)                                | Full | V          |                        | 81       |                 | dBc   |

| 100 MHz f <sub>00T</sub> (±1 MHz)                                 | Full | V          |                        | 82       |                 | dBc   |

| 100 MHz f <sub>OUT</sub> (±50 kHz)                                | Full | V          |                        | 86       |                 | dBc   |

| 180 MHz f <sub>OUT</sub> (±15 MHz)                                | Full | V          |                        | 74       |                 | dBc   |

| 180 MHz f <sub>OUT</sub> (±1 MHz)                                 | Full | V          |                        | 84       |                 | dBc   |

| 180 MHz four (±1 WHz)                                             | Full | V          |                        | 85       |                 | dBc   |

| 360 MHz f <sub>out</sub> (±35 MHz)                                | Full | V          |                        | 85<br>75 |                 | dBc   |

|                                                                   | Full |            |                        | 75<br>85 |                 | dBc   |

| 360 MHz f <sub>OUT</sub> (±1 MHz)                                 | Full | V          |                        | 85<br>86 |                 | dBc   |

| 360 MHz f <sub>OUT</sub> (±50 kHz)                                |      |            |                        |          |                 |       |

| 180 MHz f <sub>OUT</sub> (±15 MHz, 700 MHz REFCLK)                | Full | V          |                        | 65<br>80 |                 | dBc   |

| 180 MHz f <sub>OUT</sub> (±1 MHz, 700 MHz REFCLK)                 | Full | V          |                        | 80       |                 | dBc   |

| 180 MHz fout (±50 kHz, (700 MHz REFCLK)                           | Full | V          | 1                      | 84       |                 | dBc   |

| OUTPUT PHASE NOISE CHARACTERISTICS (AT 103 MHz I <sub>OUT</sub> ) |      |            |                        | 4        |                 | 15 "  |

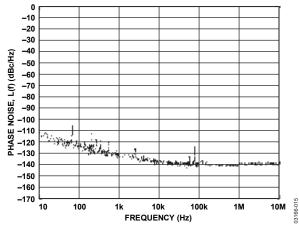

| At 1 kHz Offset                                                   | Full | V          |                        | -147     |                 | dBc/F |

| At 10 kHz Offset                                                  | Full | V          |                        | -150     |                 | dBc/F |

| At 100 kHz Offset                                                 | Full | V          | -                      | -152     |                 | dBc/F |

| OUTPUT PHASE NOISE CHARACTERISTICS (AT 403 MHz I <sub>OUT</sub> ) |      | 1.,        |                        |          |                 |       |

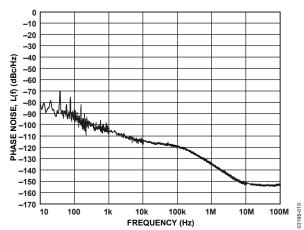

| At 1 kHz Offset                                                   | Full | V          |                        | -133     |                 | dBc/F |

| At 10 kHz Offset                                                  | Full | V          |                        | –137     |                 | dBc/F |

| At 100 kHz Offset                                                 | Full | V          |                        | -140     |                 | dBc/F |

| Parameter                                                              | Temp | Test Level | Min  | Тур | Max      | Unit     |

|------------------------------------------------------------------------|------|------------|------|-----|----------|----------|

| OUTPUT PHASE NOISE CHARACTERISTICS                                     |      |            |      |     |          |          |

| (AT 100 MHz IOUT With 700 MHz REFCLK)                                  |      |            |      |     |          |          |

| At 100 Hz Offset                                                       | Full | V          | -125 |     |          | dBc/Hz   |

| At 1 kHz Offset                                                        | Full | V          | -140 |     |          | dBc/Hz   |

| At 10 kHz Offset                                                       | Full | V          | -148 |     |          | dBc/Hz   |

| At 100 kHz Offset                                                      | Full | V          | -150 |     |          | dBc/Hz   |

| At 1 MHz Offset                                                        | Full | V          | -150 |     |          | dBc/Hz   |

| At 10 MHz Offset                                                       | Full | V          | -150 |     |          | dBc/Hz   |

| PHASE DETECTOR AND CHARGE PUMP                                         |      |            |      |     |          |          |

| Phase Detector Frequency                                               | Full | VI         |      |     | 150      | MHz      |

| Phase Detector Frequency (Divide-by-4 Enabled) <sup>3</sup>            | Full | VI         |      |     | 400      | MHz      |

| Charge Pump Sink and Source Current⁴                                   | Full | VI         |      |     | 4        | mA       |

| Fast Lock Current (Acquisition Only)                                   | Full | VI         |      |     | 7        | mA       |

| Open-Loop Current (Acquisition Only)                                   | Full | VI         |      |     | 30       | mA       |

| Sink and Source Current Absolute Accuracy⁵                             | Full | V          |      | 2.5 |          | %        |

| Sink and Source Current Matching <sup>5</sup>                          | Full | V          |      | 1   |          | %        |

| Input Sensitivity $PD_{IN}$ and $DIV_{IN}$ (50 $\Omega$ ) <sup>6</sup> | Full | IV         | -15  |     | 0        | dBm      |

| Input Impedance $PD_{IN}$ and $DIV_{IN}$ (Single-Ended)                | Full | V          |      | 1   |          | kΩ       |

| Phase Noise @ 100 MHz Input Frequency                                  |      |            |      |     |          |          |

| At 10 kHz Offset                                                       | Full | V          |      | 110 |          | dBc/Hz   |

| At 100 kHz Offset                                                      | Full | V          |      | 140 |          | dBc/Hz   |

| At 1 MHz Offset                                                        | Full | V          |      | 148 |          | dBc/Hz   |

| Charge Pump Output Range <sup>7</sup>                                  | Full | V          |      |     | $CPV_DD$ | V        |

| MIXER                                                                  |      |            |      |     |          |          |

| IF <sub>OUT</sub> <sup>8</sup>                                         | Full | V          |      | 400 |          | MHz      |

| $f_RF$                                                                 | Full | VI         |      |     | 2        | GHz      |

| $f_{LO}$                                                               | Full | VI         |      |     | 2        | GHz      |

| Conversion Gain                                                        | Full | VI         | 0.0  | 3.5 |          | dB       |

| LO Level                                                               | Full | VI         | -10  |     | +5       | dBm      |

| RF Level                                                               | Full | VI         | -20  |     |          | dBm      |

| Input IP3                                                              | Full | VI         | 5    | 9   |          | dBm      |

| 1 dB Input Compression Power <sup>9</sup>                              | Full | VI         | -3   |     |          | dBm      |

| Input Impedance (Single-Ended)                                         |      |            |      |     |          |          |

| LO                                                                     | Full | V          |      | 1   |          | kΩ       |

| RF                                                                     | Full | V          |      | 1   |          | kΩ       |

| CMOS LOGIC INPUTS                                                      |      |            |      |     |          |          |

| Logic 1 Voltage                                                        | Full | VI         | 2.0  |     |          | V        |

| Logic 0 Voltage                                                        | Full | VI         |      |     | 0.8      | V        |

| Logic 1 Current                                                        | Full | VI         |      |     | 12       | μΑ       |

| Logic 0 Current                                                        | Full | VI         |      |     | 12       | μA       |

| Input Capacitance                                                      | Full | V          |      | 3   |          | pF       |

| CMOS LOGIC OUTPUTS (1 mA LOAD)                                         |      |            |      |     |          | <u> </u> |

| Logic 1 Voltage                                                        | Full | VI         | 2.8  |     |          | V        |

| Logic 0 Voltage                                                        | Full | VI         |      |     | 0.4      | V        |

| POWER DISSIPATION                                                      |      |            |      |     |          |          |

| P <sub>DISS</sub> (Worst-Case Conditions—Everything on                 | Full | VI         |      | 2   | 2.5      | w        |

| P <sub>FD</sub> Input Frequency 150 MHz)                               |      |            |      | -   |          |          |

| P <sub>DISS</sub> (DAC and DDS Core Only Worst-Case)                   | Full | VI         |      | 1.7 | 2        | W        |

| P <sub>DISS</sub> (Power-Down Mode)                                    | Full | VI         |      | 65  | 100      | mW       |

| P <sub>DISS</sub> Mixer Only                                           | Full | VI         |      | 60  | 75       | mW       |

| P <sub>DISS</sub> PFD and CP (at 100 MHz) Only                         | Full | VI         |      | 350 | 435      | mW       |

| Parameter                                      | Temp | Test Level | Min | Тур | Max | Unit         |

|------------------------------------------------|------|------------|-----|-----|-----|--------------|

| TIMING CHARACTERISTICS                         |      |            |     |     |     |              |

| Serial Control Bus                             |      |            |     |     |     |              |

| Maximum Frequency                              | Full | IV         |     |     | 10  | MHz          |

| Minimum Clock Pulse Width Low (tPWL)           | Full | IV         | 5.5 |     |     | ns           |

| Minimum Clock Pulse Width High (tpwh)          | Full | IV         | 15  |     |     | ns           |

| Maximum Clock Rise/Fall Time                   | Full | IV         |     |     | 1   | ns           |

| Minimum Data Setup Time (t <sub>DS</sub> )     | Full | IV         | 7   |     |     | ns           |

| Minimum Data Hold Time (t <sub>DH</sub> )      | Full | IV         | 0   |     |     | ns           |

| Maximum Data Valid Time (t <sub>DV</sub> )     | Full | IV         |     |     | 20  | ns           |

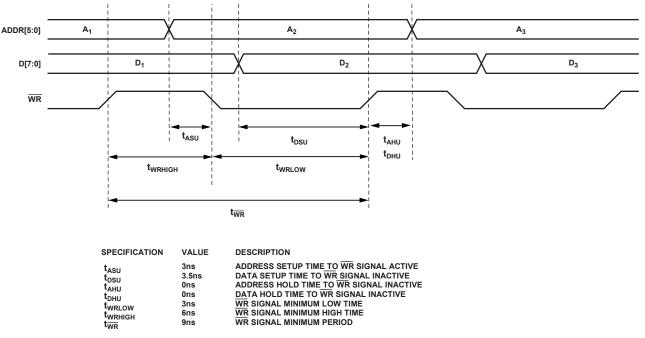

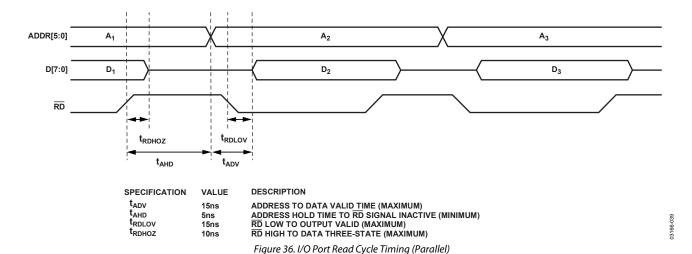

| Parallel Control Bus <sup>10</sup>             |      |            |     |     |     |              |

| WR Minimum Low Time (twrlow)                   | Full | IV         | 3   |     |     | ns           |

| WR Minimum High Time (twrhigh)                 | Full | IV         | 6   |     |     | ns           |

| WR Minimum Period (twr)                        | Full | IV         | 9   |     |     | ns           |

| Address to WR Setup (t <sub>ASU</sub> )        | Full | IV         | 3   |     |     | ns           |

| Address to WR Hold (t <sub>AHU</sub> )         | Full | IV         | 0   |     |     | ns           |

| Data to WR Setup (t <sub>DSU</sub> )           | Full | IV         | 3.5 |     |     | ns           |

| Data to WR Hold (t <sub>DHU</sub> )            | Full | IV         | 0   |     |     | ns           |

| Miscellaneous Timing Specifications            |      |            |     |     |     |              |

| REFCLK to SYNCLK                               | Full | V          |     | 2.5 |     | ns           |

| FUD/PS[1:0] to SYNCLK Setup Time <sup>11</sup> | Full | IV         | 4   |     |     | ns           |

| FUD/PS[1:0] to SYNCLK Hold Time <sup>11</sup>  | Full | IV         | 0   |     |     | ns           |

| REFCLK to SYNCLK Delay                         | Full | IV         |     | 2.5 | 3   | ns           |

| DATA LATENCY (PIPELINE DELAY)                  |      |            |     |     |     |              |

| FTW/POW to DAC Output                          | 25°C | IV         | 83  |     | 83  | SYSCL cycles |

| DFTW to DAC Output                             | 25°C | IV         | 99  |     | 99  | SYSCL cycles |

<sup>&</sup>lt;sup>1</sup> REFCLK input is internally dc biased. AC coupling should be used.

<sup>&</sup>lt;sup>2</sup> Reference clock frequency is selected to ensure that the second harmonic is out of the bandwidth of interest.

<sup>&</sup>lt;sup>3</sup> PD inputs set at 400 MHz with divide-by-4 enabled.

<sup>4</sup> The charge pump current is programmable in eight discrete steps; minimum value assumes current sharing.

<sup>5</sup> For  $0.75 \text{ V} < \text{V}_{CP} < \text{CPV}_{DD} = 0.75 \text{ V}$ .

<sup>&</sup>lt;sup>6</sup> These differential inputs are internally dc biased. AC coupling should be used.

The charge pump supply voltage can range from 4.75 V to 5.25 V. B DAC output is differential open collector. For 1 dB output compression; input power measured at 50  $\Omega$ . Describing a for timing diagrams.

<sup>&</sup>lt;sup>11</sup> See Figure 34 for timing diagram.

<sup>&</sup>lt;sup>12</sup> SYSCLK = REFCLK/x, where x is 1 or 2, as set using CFR[6].

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                    | Rating                     |

|------------------------------|----------------------------|

| Maximum Junction Temperature | 150°C                      |

| $AV_DD$                      | 4 V                        |

| $DV_{DD}$                    | 4 V                        |

| $CPV_DD$                     | 6 V                        |

| Digital Input Voltage Range  | −0.7 V to +V <sub>DD</sub> |

| Digital Output Current       | 5 mA                       |

| Storage Temperature Range    | −65°C to +150°C            |

| Operating Temperature Range  | −40°C to +85°C             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL PERFORMANCE

Table 3.

| Symbol                | Description (Using a 2S2P Test Board)                                                                       | Value (°C/W) |

|-----------------------|-------------------------------------------------------------------------------------------------------------|--------------|

| θја                   | Junction-to-ambient thermal resistance,<br>0.0 m/sec airflow per JEDEC JESD51-2<br>(still air)              | 19.8         |

| $\theta_{\text{JMA}}$ | Junction-to-ambient thermal resistance,<br>1.0 m/sec airflow per JEDEC JESD51-6<br>(moving air)             | 15.6         |

| $\theta_{JMA}$        | Junction-to-ambient thermal resistance,<br>2.0 m/sec airflow per JEDEC JESD51-6<br>(moving air)             | 14.6         |

| Өлв                   | Junction-to-board thermal resistance,<br>1.0 m/sec airflow per JEDEC JESD51-8<br>(moving air)               | 8.2          |

| θις                   | Junction-to-case thermal resistance<br>(die to heat sink) per MIL-STD-883,<br>Method 1012.1                 | 0.6          |

| $\Psi_{JT}$           | Junction-to-top-of-package<br>characterization parameter, 0 m/sec<br>airflow per JEDEC JESD51-2 (still air) | 0.15         |

The AD9858 is specified for a case temperature ( $T_{\text{CASE}}$ ). To ensure that  $T_{\text{CASE}}$  is not exceeded, an airflow source may be used.

To determine the junction temperature on the application printed circuit board (PCB),

$$T_J = T_{CASE} + (\Psi_{JT} \times PD)$$

where:

$T_I$  is the junction temperature (°C).

$T_{CASE}$  is the case temperature (°C) measured by the customer at the top center of package.

$\Psi_{JT}$  is found in Table 3.

*PD* is the power dissipation (see the total power dissipation in Table 1).

Values of  $\theta_{JA}$  are provided for package comparison and PCB design considerations.  $\theta_{JA}$  can be used for a first-order approximation of  $T_J$  by the equation

$$T_J = T_A + (\theta_{JA} \times PD)$$

where  $T_A$  is the ambient temperature (°C).

Values of  $\theta_{JB}$  are provided for package comparison and PCB design considerations (see Table 3).

Values of  $\theta_{JC}$  are provided for package comparison and PCB design considerations when an external heat sink is required (see Table 3).

#### **EXPLANATION OF TEST LEVELS**

- I. 100% production tested.

- III. Sample tested only.

- Parameter is guaranteed by design and characterization testing.

- V. Parameter is a typical value only.

- VI. Devices are 100% production tested at 25°C and guaranteed by design and characterization testing for industrial operating temperature range.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

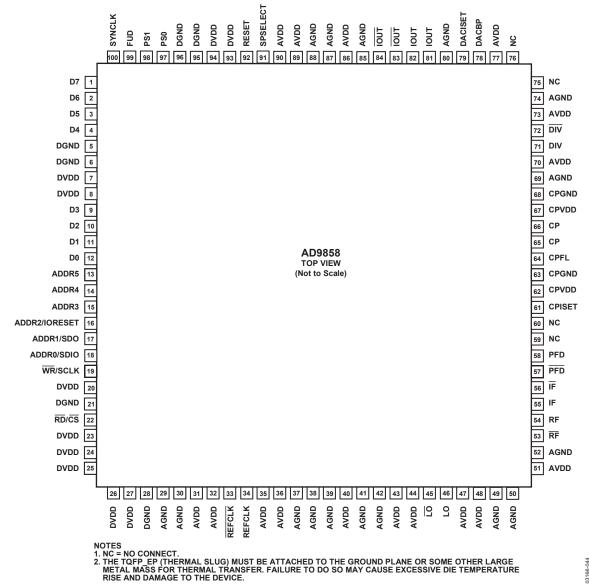

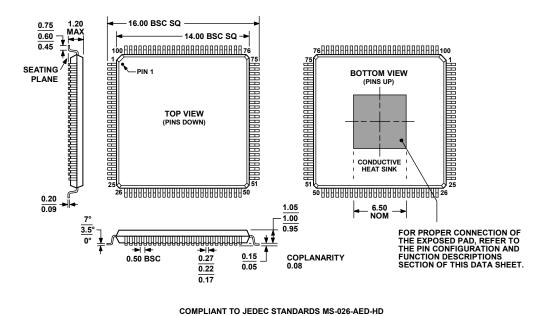

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No.                       | Mnemonic          | I/O | Description                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 4, 9 to 12               | D7 to D0          | I   | Parallel Port Data. The functionality of these pins is valid only when the I/O port is configured as a parallel port.                                                                                                                                                                                                                                               |

| 5, 6, 21, 28, 95, 96          | DGND              |     | Digitial Ground.                                                                                                                                                                                                                                                                                                                                                    |

| 7, 8, 20, 23 to 27,<br>93, 94 | DVDD              |     | Digital Supply Voltage.                                                                                                                                                                                                                                                                                                                                             |

| 13 to 18                      | ADDR5 to<br>ADDR0 | I   | When the I/O port is configured as a parallel port, these pins serve as a 6-bit address select for accessing the on-chip registers (see the IORESET, SDO, and SDIO pins for the serial port mode).                                                                                                                                                                  |

| 16                            | IORESET           | I   | This is valid for serial programming mode only. Active high input signal that resets the serial I/O bus controller. It serves as a means of recovering from an unresponsive serial bus caused by an improper programming protocol. Asserting an I/O reset does not affect the contents of previously programmed registers, nor does it invoke their default values. |

| Pin No.                                                                 | Mnemonic       | I/O | Description                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                                                                      | SDO            | 0   | This is valid for serial programming mode only. When operating the I/O port as a 3-wire serial port, this pin serves as a unidirectional serial data output pin. When operated as a 2-wire                                                                                  |

|                                                                         |                |     | serial port, this pin is unused.                                                                                                                                                                                                                                            |

| 18                                                                      | SDIO           | I/O | This is valid for serial programming mode only. When operating the I/O port as a 3-wire serial port, this pin is the serial data input. When operated as a 2-wire serial port, this pin is the bidirectional serial data pin.                                               |

| 19                                                                      | WR/SCLK        | I   | When the I/O po <u>rt</u> is configured for parallel programming mode, this pin functions as an active low write pulse (WR). When configured for serial programming mode, this pin functions as the serial data clock (SCLK).                                               |

| 22                                                                      | RD/CS          | I   | When the I/O port is configured for parallel programming mode, this pin functions as an active low read pulse (RD). When configured for serial programming mode, this pin functions as an active low chip select (CS) that allows multiple devices to share the serial bus. |

| 29, 30, 37 to 39,<br>41, 42, 49, 50, 52,<br>69, 74, 80, 85, 87, 88      | AGND           | I   | Analog Ground.                                                                                                                                                                                                                                                              |

| 31, 32, 35, 36,<br>40, 43, 44, 47,<br>48, 51, 70, 73,<br>77, 86, 89, 90 | AVDD           | I   | Analog Supply Voltage.                                                                                                                                                                                                                                                      |

| 33                                                                      | REFCLK         | 1   | Reference Clock Complementary Input. When the REFCLK port operates in single-ended mode, REFCLK should be decoupled to AVDD with a 0.1 $\mu$ F capacitor.                                                                                                                   |

| 34                                                                      | REFCLK         | 1   | Reference Clock Input.                                                                                                                                                                                                                                                      |

| 45                                                                      | ĪO             | 1   | Mixer Local Oscillator (LO) Complementary Input. When the LO port operates in single-ended mode, LO should be decoupled to AVDD with a 0.1 μF capacitor.                                                                                                                    |

| 46                                                                      | LO             | 1   | Mixer Local Oscillator (LO) Input.                                                                                                                                                                                                                                          |

| 53                                                                      | RF             | ı   | Analog Mixer RF Complementary Input. When the RF port operates in single-ended mode, RF should be decoupled to AVDD with a 0.1 µF capacitor.                                                                                                                                |

| 54                                                                      | RF             | I   | Analog Mixer RF Input.                                                                                                                                                                                                                                                      |

| 55                                                                      | IF             | 0   | Analog Mixer IF Output.                                                                                                                                                                                                                                                     |

| 56                                                                      | ĪF             | 0   | Analog Mixer IF Complementary Output.                                                                                                                                                                                                                                       |

| 57                                                                      | PFD            | ı   | Phase Frequency Detector Complementary Input. When the PFD port operates in single-ended mode, PFD should be decoupled to AVDD with a 0.1 µF capacitor.                                                                                                                     |

| 58                                                                      | PFD            | ı   | Phase Frequency Detector Input.                                                                                                                                                                                                                                             |

| 59, 60, 75, 76                                                          | NC             |     | No Connection.                                                                                                                                                                                                                                                              |

| 61                                                                      | CPISET         | 1   | Charge Pump Output Current Control. A resistor connected from CPISET to CPGND establishes the reference current for the charge pump.                                                                                                                                        |

| 62, 67                                                                  | CPVDD          | 1   | Charge Pump Supply Voltage.                                                                                                                                                                                                                                                 |

| 63, 68                                                                  | CPGND          | 1   | Charge Pump Ground.                                                                                                                                                                                                                                                         |

| 64                                                                      | CPFL           | 0   | Charge Pump Fast Lock Output.                                                                                                                                                                                                                                               |

| 65, 66                                                                  | CP             | 0   | Charge Pump Output.                                                                                                                                                                                                                                                         |

| 71                                                                      | DIV            | 1   | Phase Frequency Detector Feedback Input.                                                                                                                                                                                                                                    |

| 72                                                                      | DIV            | I   | Phase Frequency Detector Feedback Complementary Input. When the DIV port operates in single-ended mode, DIV should be decoupled to AVDD with a 0.1 µF capacitor.                                                                                                            |

| 78                                                                      | DACBP          |     | DAC Baseline Decoupling Pin. Typically bypassed to Pin 77 with a 0.1 µF capacitor.                                                                                                                                                                                          |

| 79                                                                      | DACISET        | 1   | A resistor connected from DACISET to AGND establishes the reference current for the DAC.                                                                                                                                                                                    |

| 81, 82                                                                  | IOUT           | 0   | DAC Output.                                                                                                                                                                                                                                                                 |

| 83, 84                                                                  | ĪOUT           | 0   | DAC Complementary Output.                                                                                                                                                                                                                                                   |

| 91                                                                      | SPSELECT       | I   | I/O Port Serial/Parallel Programming Mode Select Pin. Logic 0 is serial programming mode, and Logic 1 is parallel programming mode.                                                                                                                                         |

| 92                                                                      | RESET          | 1   | Active High Hardware Reset Pin. Assertion of the RESET pin forces the AD9858 to its default operating conditions.                                                                                                                                                           |

| 97, 98                                                                  | PS0, PS1       | 1   | Used to select one of the four internal profiles. These pins are synchronous to the SYNCLK output.                                                                                                                                                                          |

| 99                                                                      | FUD            | I   | Frequency Update. The rising edge transfers the contents of the internal buffer registers to the memory registers. This pin is synchronous to the SYNCLK output.                                                                                                            |

| 100                                                                     | SYNCLK<br>EPAD | 0   | Clock Output Pin. Serves as a synchronizer for external hardware. SYNCLK runs at REFCLK/8. Exposed paddle must be soldered to ground.                                                                                                                                       |

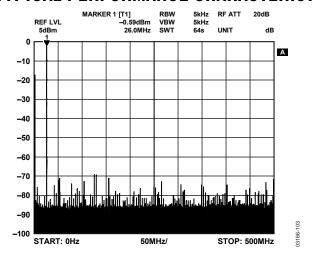

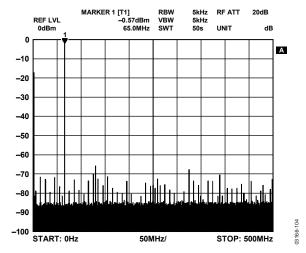

## TYPICAL PERFORMANCE CHARACTERISTICS

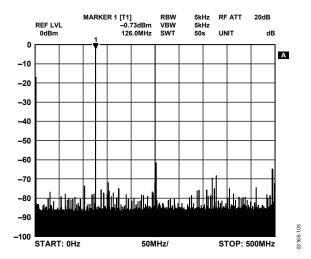

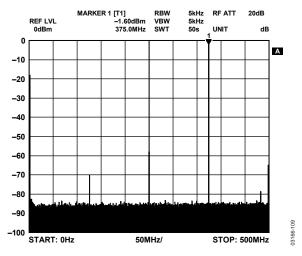

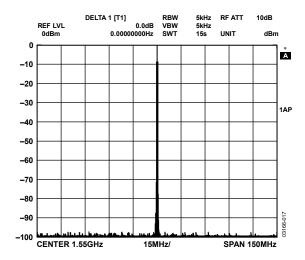

Figure 3. Wideband SFDR, 26 MHz four

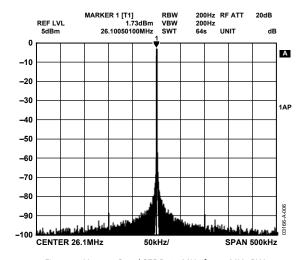

Figure 4. Wideband SFDR, 65 MHz fout

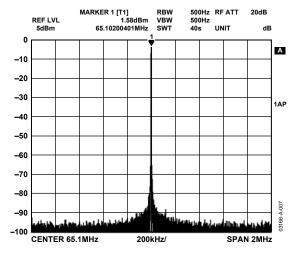

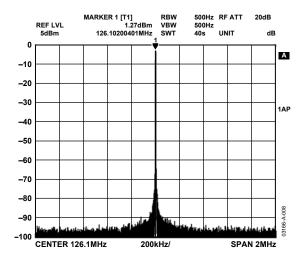

Figure 5. Wideband SFDR, 126 MHz four

Figure 6. Narrow-Band SFDR, 26 MHz fout, 1 MHz BW

Figure 7. Narrow-Band SFDR, 65 MHz  $f_{OUT}$ , 1 MHz BW

Figure 8. Narrow-Band SFDR, 126 MHz f<sub>OUT</sub>, 1 MHz BW

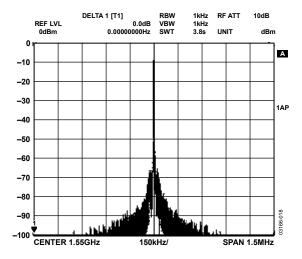

Figure 9. Wideband SFDR, 375 MHz fout

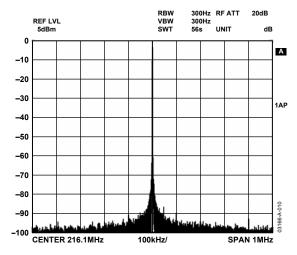

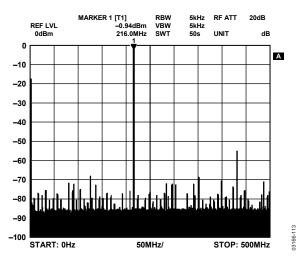

Figure 10. Narrow-Band SFDR, 216 MHz f<sub>ουτ</sub>, 1 MHz BW, 1 GHz Clock, Divider Off

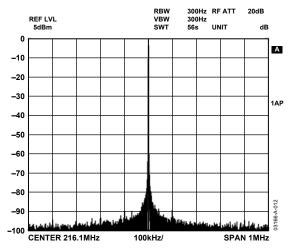

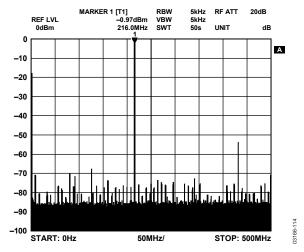

Figure 11. Narrow-Band SFDR, 216 MHz fουτ, 1 MHz BW, 2 GHz Clock, Divider On

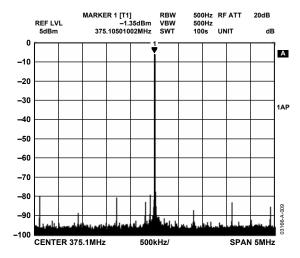

Figure 12. Narrow-Band SFDR, 375 MHz fout, 1 MHz BW

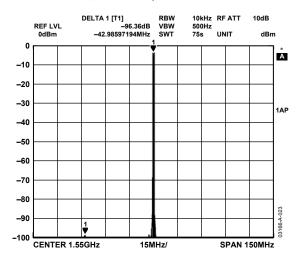

Figure 13. Wideband SFDR, 216 MHz f<sub>OUT</sub>, 1 GHz Clock, Divider Off

Figure 14. Wideband SFDR, 216 MHz f<sub>OUT</sub>, 2 GHz Clock, Divider On

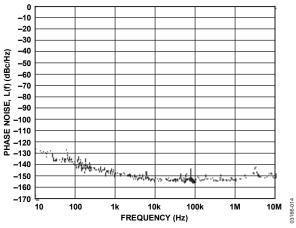

Figure 15. Residual Phase Noise, 103 MHz fout, 1 GHz REFCLK

Figure 16. Fractional Divider Loop Residual Phase Noise,  $f_{IN} = 115$  MHz,  $f_{OUT} = 1550$  MHz, Loop BW = 50 kHz

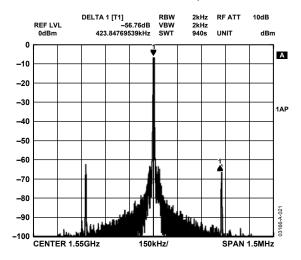

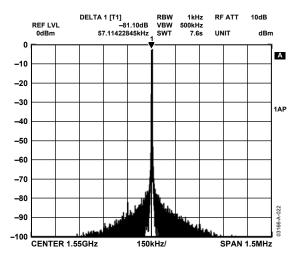

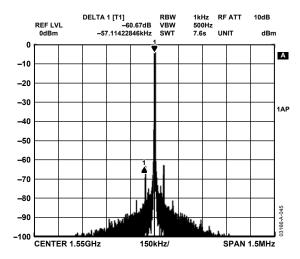

Figure 17. Fractional Divider Loop SFDR,  $f_{\rm IN}$  = 96.9 MHz,  $f_{\rm OUT}$  = 1550 MHz, BW = 1.5 MHz

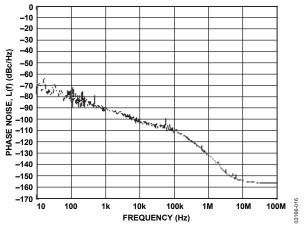

Figure 18. Residual Phase Noise, 403 MHz f<sub>Ουτ</sub>, 1 GHz REFCLK

Figure 19. Translation Loop Residual Phase Nois, e  $f_{LO} = 1500$  MHz,  $f_{OUT} = 1550$  MHz, Loop BW = 50 kHz

Figure 20. Fractional Divider Loop SFDR,  $f_{IN} = 97.3$  MHz,  $f_{OUT} = 1550$  MHz, BW = 1.5 MHz

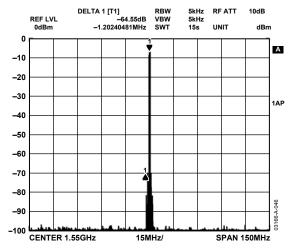

Figure 21. Fractional Divider Loop SFDR,  $f_{\text{IN}}$  = 96.9 MHz,  $f_{\text{OUT}}$  = 1550 MHz, BW = 150 MHz

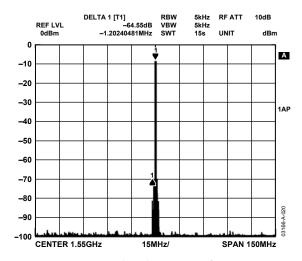

Figure 22. Translation Loop SFDR,  $f_{LO} = 1459$  MHz,  $f_{OUT} = 1550$  MHz, BW = 1.5 MHz

Figure 23. Translation Loop SFDR,  $f_{LO} = 1459$  MHz,  $f_{OUT} = 1550$  MHz, BW = 150 MHz

Figure 24. Fractional Divider Loop SFDR,  $f_{\text{IN}} = 97.3$  MHz,  $f_{\text{OUT}} = 1550$  MHz, BW = 150 MHz

Figure 25. Translation Loop SFDR,  $f_{LO}$  = 1410 MHz,  $f_{OUT}$  = 1550 MHz, BW = 1.5 MHz

Figure 26. Translation Loop SFDR,  $f_{LO} = 1410$  MHz,  $f_{OUT} = 1550$  MHz, BW = 150 MHz

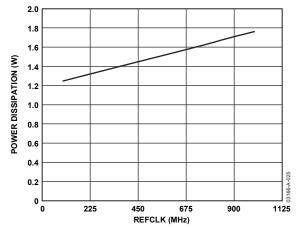

Figure 27. Power Dissipation vs. REFCLK (Single-Tone Mode,  $f_{OUT} = REFCLK/5$ )

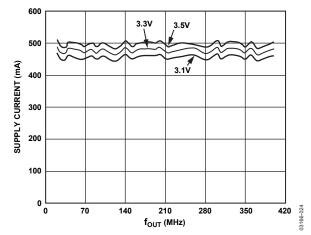

Figure 28. Supply Current vs.  $f_{OUT}$  (1 GHz REFCLK)

## THEORY OF OPERATION

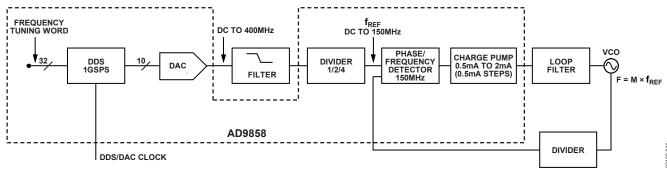

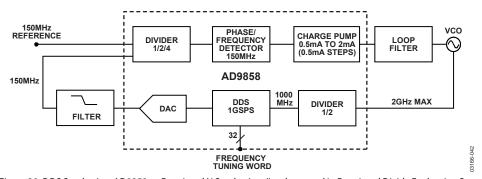

The AD9858 DDS is a flexible device that can address a wide range of applications. The device consists of a numerically controlled oscillator (NCO) with a 32-bit phase accumulator, 14-bit phase offset adjustment, a power efficient DDS core, and a 1 GSPS, 10-bit DAC. The AD9858 incorporates additional capabilities for automated frequency sweeping. The device also offers an analog mixer, a PFD, and a programmable CP with advanced fast lock capability. These RF building blocks can be used for various frequency synthesis loops or, as needed, in system design.

The AD9858 can directly generate frequencies up to 400 MHz when driven at a 1 GHz internal clock speed. This clock can be derived from an external clock source of up to 2 GHz by using the on-chip, divide-by-2 feature. The on-chip mixer, PFD, and CP make possible a variety of synthesizer configurations capable of generating frequencies in the 1 GHz to 2 GHz range or higher.

The AD9858 offers the advantages of a DDS with the additional flexibility to work in concert with analog frequency synthesis techniques (PLL, mixing) to generate precision frequency signals with high resolution, fast frequency hopping, fast settling time, and automated frequency sweeping capabilities.

Writing data to its on-chip digital registers that control all operations of the device easily configures the AD9858. The AD9858 offers a choice of serial or parallel ports for controlling the device. Four user profiles can be selected by a pair of external pins. These profiles allow independent setting of the frequency tuning word and the phase offset adjustment word for each of the four selectable configurations.

The AD9858 can be programmed to operate in single-tone mode or in frequency sweeping mode. To save on power consumption, there is also a programmable full sleep mode, during which most of the device is powered down to reduce current flow.

The operation of a direct digital synthesizer (DDS) is described in detail in a tutorial available from Analog Devices at www.analog.com/dds.

#### **COMPONENT BLOCKS**

#### **DDS** Core

The DDS core generates the numeric values that represent a sinusoid in the digital domain. Depending on the operating mode of the DDS, this sinusoid may be changed in frequency, phase, or perhaps modulated by an information carrying signal. The frequency of the output signal is determined by a user-programmed frequency tuning word (FTW). The relation of the output frequency of the device to the system clock (SYSCLK) is determined by

$$f_{OUT} = \frac{(FTW \times SYSCLK)}{2^N}$$

where N = 32.

For a more detailed explanation of a DDS core, consult the DDS tutorial at www.analog.com/dds.

#### **DAC Output**

The AD9858 includes a 10-bit current output DAC. Two complementary outputs provide a combined full-scale output current (IOUT,  $\overline{\text{IOUT}}$ ). Differential outputs reduce the amount of common-mode noise that may be present at the DAC output, offering the advantage of an increased signal-to-noise ratio (SNR). The full-scale current is controlled by means of an external resistor (R\_SET) connected between the DACISET pin and analog ground. The full-scale current is proportional to the resistor value as

$$R_{SET} = 39.19/I_{OUT}$$

The maximum full-scale output current of the combined DAC outputs is 40 mA, but limiting the output to 20 mA provides the best spurious-free dynamic range (SFDR) performance. The DAC output compliance range is (AV $_{\rm DD}-1.5$  V) to (AV $_{\rm DD}+0.5$  V). Voltages developed beyond this range cause excessive DAC distortion and can damage the DAC output circuitry. Proper attention should be paid to the load termination to keep the output voltage within this compliance range. When terminating the differential outputs into a transformer, the center tap should be attached to AVDD.

## **PLL Frequency Synthesizer**

The PLL frequency synthesizer is a group of independent synthesis blocks designed to be used with the DDS to expand the range of synthesis applications. These blocks are a digital PFD that drives a CP. The charge pump incorporates fast locking logic, described in the Fast Locking Logic section. Based on system requirements, the user supplies an external loop filter and VCO. A high speed analog mixer is included for translation synthesis loops. Using the different blocks in the PLL frequency synthesizer, in conjunction with the DDS, the user can create translation loops (also known as offset loops), fractional divider loops, and traditional PLL loops to multiply the output of the DDS in frequency.

#### Phase Frequency Detector (PFD)

The phase frequency detector has two inputs:  $PD_{IN}$  and  $DIV_{IN}$ . Both are analog inputs that can operate in differential mode or single-ended mode. Both operate at frequencies up to 150 MHz, although signals of up to 400 MHz can be accommodated on the inputs when the divide-by-4 functions are used. The expected input level for both  $PD_{IN}$  and  $DIV_{IN}$  is in the range of 800 mV p-p (differential) and 400 mV p-p (single-ended). A programmable divider that offers division ratios of M, N = {1, 2, 4} immediately follows the input. The division ratio is controlled by means of the control function register.

#### Charge Pump (CP)

The charge pump output reference current is determined by an external resistor (~2.4 k $\Omega$ ), which establishes a 500  $\mu$ A maximum internal baseline current (I<sub>CP0</sub>). The baseline current is scaled to provide the appropriate drive current for the various operating modes (frequency detect, wide closed-loop, and final closed-loop) of the CP. The amount of scaling in each mode is programmable by means of the values stored in the control function register, giving the user maximum flexibility of the frequency locking capability of the PLL.

The CP polarity can be configured as either positive or negative with respect to  $PD_{IN}$ . When the CP polarity is positive, if  $DIV_{IN}$  leads  $PD_{IN}$ , the charge pump attempts to decrease the voltage at the VCO control node. If  $DIV_{IN}$  lags  $PD_{IN}$ , the charge pump works to increase the voltage at the VCO control node. When the CP polarity is negative, the opposite occurs. This allows the user to define either input as the feedback path. This also allows the AD9858 to accommodate ground-referenced or supply-referenced VCOs. This functionality is defined by the charge pump polarity bit in the control function register, CFR[10].

Internal to the CP, the  $I_{\text{CPO}}$  current is scaled to provide different output drive current values for the various modes of operation. In normal operating mode, the final closed-loop mode can be programmed to scale  $I_{\text{CPO}}$  by 1, 2, 3, or 4. Setting the charge pump current offset bit, CFR[13], applies a 2 mA offset to the programmed charge pump current, allowing  $I_{\text{CPO}}$  scaler values of 5, 6, 7, or 8. The wide closed-loop mode can be programmed to scale  $I_{\text{CPO}}$  by 0, 2, 4, 6, 8, 10, 12, or 14. The frequency detect mode can be programmed to scale  $I_{\text{CPO}}$  by 0, 20, 40, or 60. The different modes of operation, controlled by the fast locking logic, are discussed in the Fast Locking Logic section.

The CP has an independent set of power pins that can operate at up to 5.25 V. While the device can operate from ground to rail, the voltage compliance should be kept in the 0.5 V to 4.5 V range to ensure the best steady-state performance. The combination of programmable output current, programmable polarity, wide compliance range, and a proprietary fast lock capability offers the flexibility necessary for the digital PLL to operate within a broad range of PLL applications.

### **Fast Locking Logic**

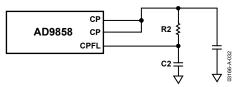

The charge pump includes a fast locking algorithm that helps to overcome the traditional limitations of PLLs with regard to frequency switching time. The fast locking algorithm works in conjunction with the loop filter shown in Figure 29 to provide extremely fast frequency switching performance.

Based on the error seen between the feedback signal and the reference signal, the fast locking algorithm puts the charge pump into one of three states: frequency detect mode, a wide closed-loop mode, or a final closed-loop mode. In the frequency detect mode, the feedback and reference signals register substantial phase and frequency errors. Rather than operating in a continuous closed-loop feedback mode, the charge pump supplies a fixed current of the correct polarity to the VCO control node that drives the loop towards frequency lock. When frequency lock is detected, the fast locking logic shifts the part into one of the closed-loop modes. In the closed-loop modes, either wide or final, the charge pump supplies current to the loop filter as directed by the PFD. The frequency detect mode is intended to bring the system to a level of frequency lock from which the intermediary closed-loop system can quickly achieve phase lock.

The level of frequency lock accuracy aimed for is typically referred to as the lock range. When the frequency is within the lock range, the time required to achieve phase lock can be determined by standard PLL transient analysis methods. The charge pump current sources associated with the frequency detect mode are connected to Pin 64 (CPFL), and the closed-loop current sources are connected to Pin 65 (CP) and Pin 66 (CP). Pin 64 is connected directly to the loop filter zero compensation capacitor, as shown in Figure 29. This connection allows the smoothest transition from the frequency detect mode to the closed-loop modes and enables faster overall switching times. Pin 65 and Pin 66 are connected to the loop filter in the conventional manner.

Figure 29. Charge Pump to Loop Filter Connection

The frequency detection block works as follows. The comparison logic in the frequency detection circuitry operates one eighth of the DDS system clock. A comparison is made of the frequencies present at  $PD_{IN}$  and  $DIV_{IN}$  over 19 DDS clock cycles.

To ensure that frequency lock detection is achieved while the frequency difference is within the PLL lock range, the slew rate of the VCO input should be limited such that the lock range cannot be traversed within 152 system clock cycles. The slew rate of the VCO input is determined by the programmed level of frequency detect current and the size of the zero compensation capacitor according to the following relationship:

$$\frac{dv}{dt} = \frac{I_{f_{det}}}{C_Z}$$

When frequency detection occurs, the loop is closed and the loop is locked based on the current programmed for the wide closed-loop mode. It is important that the loop be designed for closed-loop stability while in the wide closed-loop mode. In this mode, less phase margin can usually be tolerated, because this mode is only used to enhance the lock time but is not used in the locked free running state. When the wide closed-loop mode achieves phase lock as determined by an internal lock detector, the phase detector/charge pump transitions into the final closed-loop state. If no wide closed-loop current is programmed, the loop transitions directly from the frequency detect mode into the final closed-loop state. In the final closed-loop state, optimize the loop characteristics for the desired free running loop bandwidth.

The frequency detect mode is primarily useful in offset or translation loop applications where the phase detector inputs are more likely to detect large frequency transitions. For loop applications with significant amounts of division in the feedback loop, the frequency detection mode may not activate. This is due to the limited amount of frequency difference that is experienced at the phase detector inputs. For these applications, the primary means of accelerating the frequency settling time is to design the loop to acquire lock with the wide closed-loop setting and then switch to the final closed-loop setting.

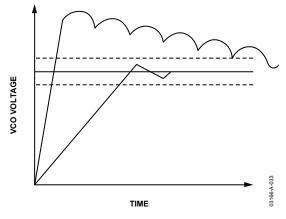

As previously mentioned, care should be taken when planning for a large transition using the frequency detect mode to ensure that the charge pump does not cause the VCO to overshoot the closed-loop lock range, because cycle slipping can occur, which results in extended delays. Figure 30 shows two system responses. In the first response, the charge pump output current is maximized during the frequency detect mode so that, after 152 clock cycles, the VCO voltage exceeds the closed-loop lock range. The second system response provides less current during the frequency detect mode. Although this results in a longer delay in approaching the closed-loop lock range, because the system does not exceed the closed-loop range, the fast locking logic shifts the charge pump into intermediary closed-loop mode, resulting in a shorter overall frequency switching time.

Figure 30. Typical Charge Pump Responses

#### Analoa Mixer

The analog mixer is included for translation loops, also known as offset loops. The radio frequency (RF) and local oscillator (LO) inputs are designed to operate at frequencies up to 2 GHz. Both inputs are differential analog input stages. Both input stages are internally dc biased and should be connected through an external ac coupling mechanism. The expected input level is in the range of 800 mV p-p (differential). The intermediate frequency (IF) output is a differential analog output stage designed to operate at frequencies less than 400 MHz. This mixer is based on the Gilbert cell architecture.

#### **MODES OF OPERATION**

The AD9858 DDS section has three modes of operation: single tone, frequency sweeping, and full sleep. The RF building blocks (PFD, CP, and mixer) can be active or powered down, used or unused, in the active modes.

In the single-tone mode, the device generates a single output frequency determined by a 32-bit word (frequency tuning word, FTW) loaded to an internal register. This frequency can be changed as desired, and frequency hopping can be accomplished at a rate limited only by the time required to update the appropriate registers. If even faster hopping is needed, the four profiles allow rapid hopping among the four frequencies stored in them by means of external select pins.

The frequency sweeping mode allows for the automation of most of the frequency sweeping task, making chirp and other frequency sweeping applications possible without multiple register operations via the I/O port.

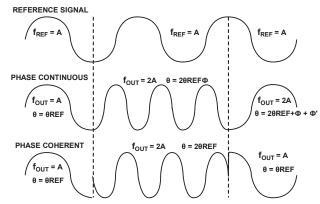

In whatever mode the device is operating, changes in frequency are phase continuous (they do not cause discontinuities in the phase of the output signal). The first phase value after a frequency change is an increment of the last phase value before the change, but at the phase increment value (FTW) of the new tuning word. (This is not the same as phase coherent over frequency changes; see Figure 31.)

WHERE  $\theta$  = PHASE OF OUTPUT SIGNAL,  $\Phi$  = PHASE AT TIME OF FIRST FREQUENCY TRANSITION, AND  $\Phi$ ' = PHASE AT TIME OF SECOND FREQUENCY TRANSITION.

Figure 31. Difference Between a Phase Continuous Frequency Change and a Phase Coherent Frequency Change

### Single-Tone Mode

When in single-tone mode, the AD9858 generates a signal, or tone, of a single desired frequency. This frequency is set by the value loaded by the user into the chip's FTW register. This frequency can be between 0 Hz and somewhat below one-half of the DAC sampling frequency (SYSCLK). One-half of the sampling frequency is commonly called the Nyquist frequency. The practical upper limit to the fundamental frequency range of a DDS is determined by the characteristics of the external low-pass filter, known as the reconstruction filter, which must follow the DAC output of the DDS. This filter reconstructs the desired analog sine wave output signal from the stream of sampled amplitude values output by the DAC at the sample rate (SYSCLK).

A DDS is a sampled data system. As the fundamental frequency of the DDS approaches the Nyquist frequency, the lower first image approaches the Nyquist frequency from above. As the fundamental frequency approaches the Nyquist frequency, it becomes difficult, and finally impossible, to design and construct a low-pass filter that provides adequate attenuation for the first image frequency component.

The maximum usable frequency in the fundamental range of the DDS is typically between 40% and 45% relative to the SYSCLK frequency, depending on the reconstruction filter. With a 1 GHz SYSCLK, the AD9858 is capable of producing maximum output frequencies of between 400 MHz and 450 MHz, depending on the reconstruction filter and the application system requirements.

For a desired output frequency ( $f_{\text{OUT}}$ ) and sampling rate (SYSCLK), the FTW of the AD9858 is calculated by

$$FTW = (f_{OUT} \times 2^{N})/SYSCLK$$

where

*N* is the phase accumulator resolution in bits (32 in the AD9858). *SYSCLK* is in Hertz.

FTW is a decimal number.

When the decimal number is calculated, it must be rounded to an integer and converted to a 32-bit binary value. The frequency resolution of the AD9858 is 0.233 Hz when the SYSCLK is 1 GHz.

#### Frequency Sweeping Mode

The AD9858 provides an automated frequency sweeping capability. This allows the AD9858 to generate frequency swept signals for chirped radar or other applications. The AD9858 includes features that automate much of the task of executing frequency sweeps.

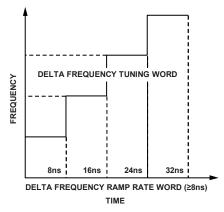

The frequency sweep feature is implemented through the use of a frequency accumulator (not to be confused with the phase accumulator). The frequency accumulator repeatedly adds an incremental quantity to the current FTW, thereby creating new instantaneous frequency tuning words, causing the frequency generated by the DDS to change with time. The frequency increment, or step size, is loaded into the delta frequency tuning word (DFTW) register. The rate at which the frequency is incremented is set by the delta frequency ramp rate word (DFRRW) register. Together these registers enable the AD9858 to sweep from a beginning frequency set by the FTW, upwards or downwards, at a desired rate and frequency step size. The result is a linear frequency sweep or chirp.

The DFRRW functions as a countdown timer, in which the value of the DFRRW is decremented at the rate of SYSCLK/8. This means that the most rapid frequency word update occurs when a value of 1 is loaded into the DFRRW and results in a frequency increment at 1/8 of the SYSCLK rate. With a SYSCLK of 1 GHz, the frequency can be incremented at a maximum rate of 125 MHz (DFRRW = 1). The DFTW must specify whether the frequency sweep should proceed up or down from the starting frequency (FTW). Therefore, the DFTW is expressed as a twos complement binary value, in which positive indicates up and negative indicates down.

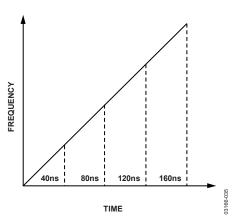

Figure 32. Frequency vs. Time Plots for a Given Sweep Profile

A DFRRW value of 0 written to the register stops all frequency sweeping. There is no automated stop-at-a-given-frequency function. The user must calculate the time interval required to reach the final frequency and then issue a command to write 0 into the DFRRW register. The time required for a frequency sweep is calculated by

$$t = \frac{\left| f_F - f_S \right| \times 2^{34}}{\text{SYSCLK}^2} \times \frac{DFRRW}{DFTW}$$

where:

*T* is the duration of the sweep in seconds. *f*<sub>S</sub> is the starting frequency determined by

$$f_{S} = \frac{FTW}{2^{32}} \times SYSCLK$$

$f_F$  is the final frequency.

The delta frequency step size is given by

$$\Delta f = \frac{DFTW \times SYSCLK}{2^{31}},$$

remembering that DFTW is a signed (twos complement) value.

The time between each frequency step ( $\Delta t$ ) is given by

$$\Delta t = \frac{8 \times DFRRW}{SYSCLK}$$

The value of the stop frequency  $f_F$  is determined by

$$f_F = f_S + t \times \frac{\Delta f}{\Delta t}$$

## **Returning to Starting Frequency**

The original frequency tuning word (FTW), which is written into the frequency tuning register, does not change at any time during a sweep operation. This means that the DDS can return to the sweep starting frequency at any time during a sweep. Setting the control bit, autoclear frequency accumulator, forces the frequency accumulator to 0, instantly returning the DDS to the frequency stored as FTW.

#### Full Sleep Mode

Setting all of the power-down bits in the control function register activates full sleep mode. During the power-down condition, the clocks associated with the various functional blocks of the device are turned off, thereby offering a significant power savings.

#### **SYNCHRONIZATION**

#### SYNCLK and FUD Pins

Timing for the AD9858 is provided via the user-supplied REFCLK input. The REFCLK input is buffered and is the source for the internally generated SYSCLK. The frequency of SYSCLK can be either the same as REFCLK or half that of REFCLK (CFR[6]). The REFCLK input is capable of handling input frequencies as high as 2 GHz. However, the device is designed for a maximum SYSCLK frequency of 1 GHz. Thus, it is mandatory that the divide-by-2 SYSCLK function be enabled when the frequency of REFCLK is greater than 1 GHz.

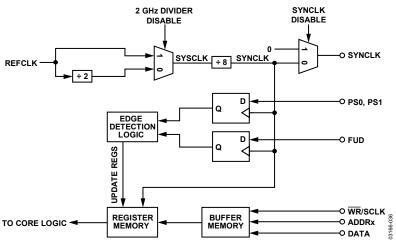

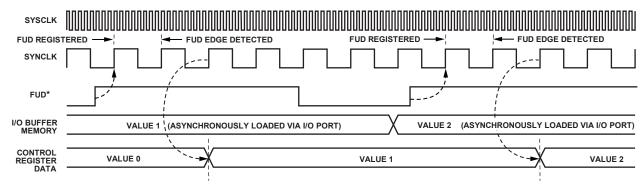

SYSCLK serves as the sample clock for the DAC and is fed to a divide-by-8 frequency divider to produce SYNCLK. SYNCLK is provided to the user on the SYNCLK pin. This enables synchronization of external hardware with the internal DDS clock of the AD9858. External hardware that is synchronized to the SYNCLK signal can then be used to provide the frequency update (FUD) signal to the AD9858. The FUD signal and SYNCLK are used to transfer the internal buffer register contents into the memory registers of the device. Figure 33 shows a block diagram of the synchronization methodology, and Figure 34 shows an I/O synchronization timing diagram.

SYNCLK is also used to synchronize the assertion of the profile select pins (PS0 and PS1). The FUD, PS0, and PS1 pins must be set up and held around the rising edge of SYNCLK.

Figure 33. I/O Synchronization Block Diagram

\*FUD IS AN INPUT PROVIDED BY THE USER THAT MUST BE SET UP AND HELD AROUND RISING EDGES OF SYNCLK. THE OCCURRENCE OF THE RISING EDGE OF SYNCLK DURING THE HIGH STATE OF THE UPDATE REGS SIGNAL CAUSES THE BUFFER MEMORY CONTENTS TO BE TRANSFERRED INTO THE CONTROL REGISTERS. SIMILARLY, A STATE CHANGE ON THE PS0 OR PS1 PIN IS EQUIVALENT TO ASSERTING A VALID FUD SEQUENCE. NOTE: I/O UPDATES ARE SYNCHRONOUS TO THE SYNCLK SIGNAL, REGARDLESS OF THE SYNCHRONIZATION MODE SELECTED.

Figure 34. I/O Synchronization Timing Diagram

### **Frequency Planning**

To achieve the best possible spurious performance when using the AD9858 in a hybrid synthesizer configuration, employ frequency planning. Frequency planning consists of being aware of the mechanisms that determine the location of the worst-case spurs and then using the appropriate loop tuning parameters to place these spurs either outside the loop bandwidth, so that they are attenuated, or completely outside the frequency range of interest.

When using the fractional divider configuration, the worst-case spurs occur whenever the images of the DAC harmonics fold back such that they are close to the DAC fundamental or carrier frequency. If these images fall within the loop bandwidth, they are gained up by approximately  $20 \times \log N$ , where N is the gain in the loop. If N is relatively high, these spurs can still realize significant gain, even if they are slightly outside the loop bandwidth, because the loop attenuation rate is typically 20 dB/dec in this region. DAC images occur at

$$N \times f_{CLOCK} \pm M \times f_{OUT}$$

where N and M are integer multiples of  $f_{CLOCK}$  and  $f_{OUT}$ , respectively.

Figure 20 shows a high spurious condition where the low-order odd harmonics are folding back around the fundamental. Figure 24 shows that the worst spurs are confined to a narrow region around the carrier and that wideband spurs are attenuated. Figure 17 shows an alternate frequency plan that results in the same carrier frequency. The output frequency of the DAC is set by

$$f_{OUT} = f_{CLOCK} \times FTW/2^{N}$$

This makes it possible to produce the same  $f_{\text{OUT}}$  by different combinations of  $f_{\text{CLOCK}}$  and FTW. In this case, the worst DAC spurs are placed well outside the loop bandwidth such that they are attenuated below the noise floor. Figure 21 shows a wideband plot for this frequency plan.

Other frequency combinations that result in high spurious signals are when subharmonics of  $f_{\rm CLOCK}$  fall within or near the loop bandwidth. To avoid this, ensure that the DAC  $f_{\rm OUT}$  is sufficiently offset from the subharmonics of  $f_{\rm CLOCK}$  such that these products are attenuated by the loop.